Overview

The summer school is organized by the Technical University of Denmark (DTU) in collaboration with Edu4Chip partner institutions and will take place in Denmark at the Technical University of Denmark campus in Kongens Lyngby (near Copenhagen).

The summer school is structured into two main parts:

- Online intro-day (August 11th) - Covering fundamental concepts in chip and digital design, with interactive exercises and project introductions.

- In-person program (August 18th to 22nd) - Held at DTU in Denmark, featuring in-depth lectures, hands-on activities, keynotes, and social events.

Target audience and scope

The summer school is designed for Bachelor students and Master students with a background in electrical engineering, computer science and engineering, or physics, the summer school emphasizes practical learning activities. PhD students are also welcome. Participants will acquire foundational knowledge of chip design workflows, develop skills in tools and methodologies, and explore cutting-edge developments in the field.

ECTS credit transfer and financial support

The Edu4Chip Summer School is organized within the framework of the Erasmus Blended Intensive Program (BIP), which allows for credit transfer among participating institutions. Upon successful completion within the BIP, students can be awarded 3 ECTS credits. For students enrolled at DTU, the summer school can be integrated into a more extensive 3-week special course, allowing them to earn 5 ECTS credits.

For details on financial support options, especially for students from Erasmus partner institutions and Edu4Chip partners, please refer to the Financial Support section.

Additional sponsorship

In addition to the EU financial support the summer school is co-sponsored by the Danish Chip Competence Center.

Practical information

Please find below some practial information realted to location, accomodation, and transport.

Location

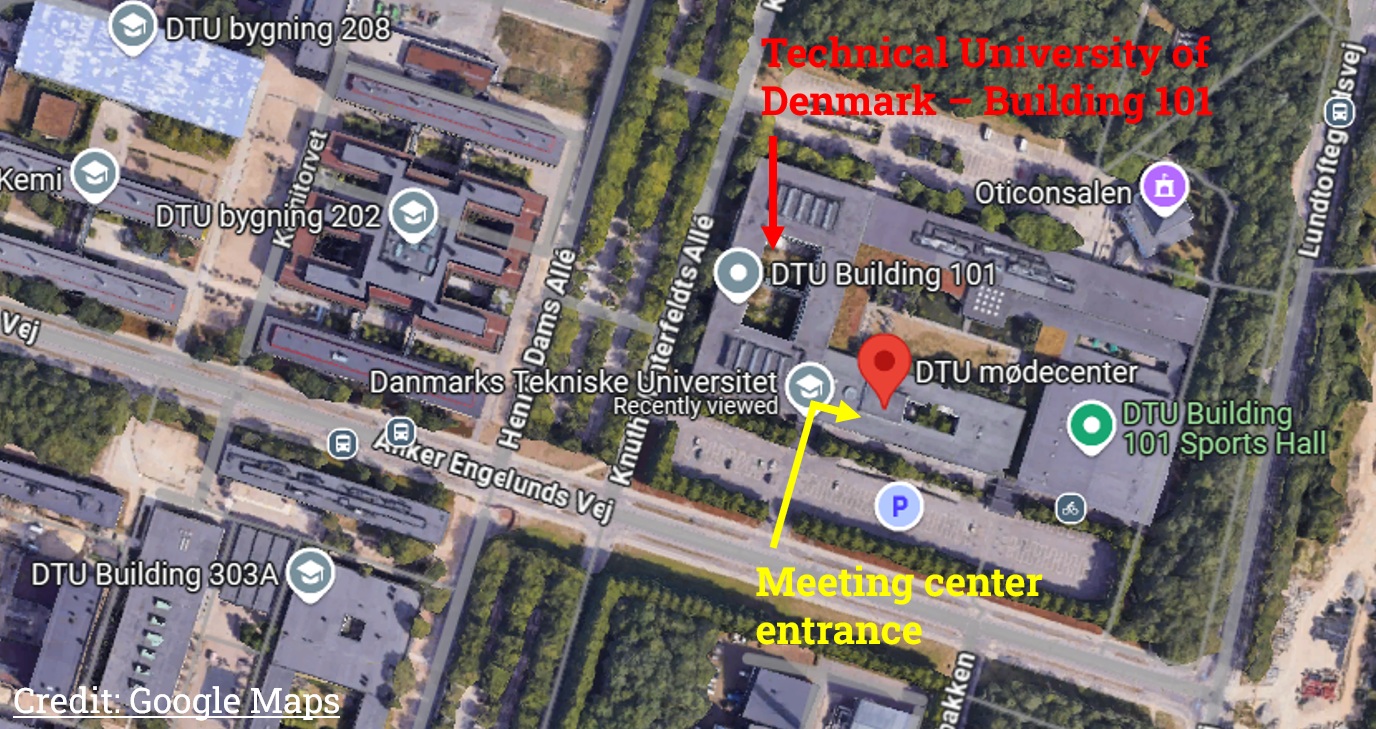

The Edu4Chip Summer School will take place at the Technical University of Denmark (DTU) in Kongens Lyngby, a town located just north of Copenhagen.

- Venue: Technical University of Denmark Meeting Center, Building 101, Room S09

- Address: Anker Engelunds Vej 1, 2800 Kongens Lyngby

- Google Maps link: View location

To help you get oriented, here is a map showing the location of DTU in Kongens Lyngby. This should give you a better sense of the surrounding area and help you plan your accommodation and travel accordingly.

Accommodation

DTU does not offer on-campus accommodation for summer school participants. Each student is responsible for arranging their own accommodation independently. We recommend searching through popular platforms such as Booking.com, Airbnb, or similar services to find lodging that fits your preferences and budget.

You may choose to stay near the university in Kongens Lyngby for convenience, or in Copenhagen if you prefer a more urban environment. Important: In general public transport is feasable from either location. However, before booking your accommodation, we recommend checking public transport routes to and from DTU. Some places that appear geographically close to the university may not be conveniently connected by public transport. See the next section for more information about transport options.

Transport

If you're arriving from abroad, the nearest airport is Copenhagen Airport (CPH), which is well-connected to the city center by the Metro. The journey from the airport to central Copenhagen typically takes around 15-20 minutes.

The summer school venue in Kongens Lyngby is connected to Copenhagen via the S-train (commuter train) and several bus lines. The commute from central Copenhagen to Lyngby takes approximately 30 minutes. Public transport in the Greater Copenhagen area is reliable, safe, and frequent.

We suggest using tools such as Google Maps or Rejseplanen.dk to explore travel options and find the best routes and timetables.

A map of the train lines and information about tickets and fares is also available at DSB's official website.

Useful tips

Bring your laptop and charger: You will need a laptop for the summer shcool program. Denmark uses Type C or K plugs (EU standard, 230 V), check if you need an adapter.

Dress smart for unpredictable weather: Copenhagen summer temperatures can range from 10°C to 28°C. Bring different layers (T-shirts, sweaters, a light jacket) to adapt easily throughout the day. Pack a small umbrella or a waterproof jacket, and consider water-resistant shoes or quick-drying clothing.

Other handy items: Sunscreen (hopefully we might need it!), and a notebook/pen for quick notes and drafts.

Program and content

Over six days, including the online introductory day, participants will engage in lectures, hands-on exercises, and keynotes delivered by leading academics and industry experts. The program highlights topics such as agile hardware design, analog/mixed-signal circuits, verification techniques, and asynchronous circuits.

The Edu4Chip Summer School is structured into two main parts: an Online intro-day and an In-person program in Copenhagen. Find below the schedule, and a detailed description of the content of the online intro-day, in-person lectures, keynotes, and other activities, as well as the learning objectives.

Schedule

Online intro-day - Monday, August 11th

Teacher for the day: Assoc. Prof. Luca Pezzarossa (Technical University of Denmark)09:30 - 12:00

- Welcome

- Introduction to the summer school

- Q&A and discussion session

- Participant attendance check-in

- Brush-up on Digital Design

12:00 - 13:00

- Lunch break

13:00 - 14:00

- Brush-up on Digital Design (continues)

14:00 - 16:00

- Exercises

16:00 - 16:30

- Outline of the student project

- Participant attendance check-out

16:30 - 17:00

- Q&A and discussion session

In-person day 1 - Monday, August 18th

10:00 - 10:15

- Registration and coffee/breakfast

10:15 - 11:10

- Welcome from the organizers

- Summer school introduction and overview

- Welcome message from Prof. Jan Madsen, Head of Department at DTU Compute

11:10 - 12:00

- Presentation: A Nordic and European perspective on chips, by Claus Friis Pedersen (Danish Chip Competence Center) and Lars Palm (Swedish Chip Competence Center)

12:00 - 13:00

- Lunch served at the summer school location

13:00 - 13:50

- Keynote: From the 1st transistor to FinFETs, and beyond, by Assoc. Prof. Flemming Stassen (Technical University of Denmark)

13:50 - 14:00

- Break

14:00 - 15:00

- Presentation: The Edu4Chip project, by Edu4Chip partners

15:00 - 15:15

- Break: Coffee and refreshments

15:15 - 17:00

- Lecture: Chip design process overview, by Univ. Instuctor Arto Oinonen and Doctoral Researcher Matti Käyrä (Tampere University)

17:00 - 18:00

- Quickfire introduction of students

In-person day 2 - Tuesday, August 19th

09:00 - 12:00

- Lecture & hands-on session: Agile hardware design in HDL, by Prof. Martin Schoeberl (Technical University of Denmark)

- Break for coffee and refreshments at 10:30

12:00 - 13:00

- Lunch at the kantine in Building 202. Google Maps link: View location

13:00 - 13:50

- Keynote: Design for low-power ICs for hearing instruments, by Evangelia Kasapaki and Vijay Kumar Bhat (Demant)

13:50 - 14:00

- Break

14:00 - 17:00

- Lecture & hands-on session: Systems-on-chip and interconnects, by Assoc. Prof. Luca Pezzarossa (Technical University of Denmark)

- Break for coffee and refreshments at 15:00

17:10 - 19:30

- Picnic on DTU premises

- Location: Wicked Rabbit Kantine in Building 342. Google Maps link: View location

In-person day 3 - Wednesday, August 20th

09:00 - 12:00

- Lecture & hands-on session: Time-discrete analog circuits, by Dipl.-Ing. (Univ.) Markus Dietl (Technical University of Munich)

- Break for coffee and refreshments at 10:30

12:00 - 13:00

- Lunch served at the summer school location

13:00 - 16:00

- Lecture & hands-on session: Verification of digital circuits, by Jacob Sander Andersen (Syosil)

- Break for coffee and refreshments at 14:30

16:00 - 19:00

- Walking tour of Copenhagen (bring an umbrella!)

- Bus to Copenhagen departs at 16:10 from outside Building 101 (summer school location)

19:00 - 20:45

- Dinner in Copenhagen

- Location: Restaurant Sult i Cinemateket, Vognmagergade 8B, 1120 København K. Google Maps link: View location

In-person day 4 - Thursday, August 21st

09:00 - 12:00

- Lecture & hands-on session: Chip design process and challenges, by Assist. Prof. Ole Richter (Technical University of Denmark)

- Break for coffee and refreshments at 10:30

12:00 - 13:00

- Lunch at the kantine in Building 202. Google Maps link: View location

13:00 - 13:50

- Keynote: "Basic concepts in modeling" - A discussion of George Box's famous statement 'All models are wrong, some are useful' with a strong focus on models in chip design, by Prof. Dr.-Ing. Wolfgang Ecker (Infineon / Technical University of Munich)

13:50 - 14:00

- Break

14:00 - 17:00

- Lecture - advanced topics: Asynchronous circuits, by Emeritus Prof. Jens Sparsø (Technical University of Denmark)

- Lecture - advanced topics: Formal verification, by Prof. Oliver Keszöcze (Clausthal University of Technology)

- Lecture - advanced topics: LEGO inspired chip design, by Prof. Ahmed Hemani (KTH Royal Institute of Technology)

- Break for coffee and refreshments at 15:00

17:00 - 19:00

- Project work (preparation of the student presentations)

In-person day 5 - Friday, August 22nd

09:00 - 12:00

- Student presentations (count as exam)

- Coffee and refreshments at 09:00

12:00 - 13:00

- Lunch served at the summer school location

13:00 - 14:00

- Summer school wrap-up

- Farewell

Content of the online intro-day (August 11th)

The online into-day provides an overview of the Edu4Chip Summer School, covering fundamental concepts in chip and digital design. Participants will engage in interactive exercises and receive guidance on the student project to prepare for the in-person sessions. Find below a summary of the intro-day activities.

-

Introduction to the summer school

An overview of the summer school, its objectives, and an introduction to the program, participants, and instructors. -

Brush-up on digital design

A refresher session focusing on essential digital design concepts to ensure all participants are aligned with the foundational knowledge. -

Interactive web-based exercises

Hands-on activities where participants will design and simulate an integrated circuit using open-source tools. -

Outline of the student project

Introduction to the student project, detailing objectives and expected outcomes. Projects will be carried out during the summer school. -

Q&A and discussion session

An interactive session for participants to engage with instructors, ask questions, and discuss key topics covered throughout the day and planned for the physical part of the summer school.

Content of the in-person program (August 18th to 22nd)

The in-person program offers a blend of keynotes, lectures, and hands-on activities. In addition to the lectures and keynotes, we also planned some activities to connect, relax, and explore both the academic environment and the vibe of Copenhagen. Find the details below.

Presentations and keynotes

A Nordic and European perspective on chips

by Claus Friis Pedersen (Danish Chip Competence Center) and Lars Palm (Swedish Chip Competence Center)

This opening presentation gives an introduction to the new opportunities emerging within the European chips eco-system chip as a result of increased European focus and cooperation, e.g. within the framework of the Chips Joint Undertaking (ChipsJU). The key elements of ChipsJu such as Pilotlines, Design Tool and Chips Competence Centers will be introduced. The presentation will then focus on how this is implemented in the Nordic countries and the specific opportunities this can provide to companies, academia, employees and students who are active in the chips area.

Claus Friis Pedersen is heading the Danish Chips Competence Centre. He has a back-ground in commercial deep-tech and business development in various industries including Photonics, Renewable energy, and Chips for Quantum Information processing. |

The Edu4Chip project

by Dr.-Ing. habil. Michael Pehl (Technical University of Munich), Univ. Instuctor Arto Oinonen (Tampere University), Prof. Jean-Max Dutertre (Institut Mines-Télécom), Prof. Ahmed Hemani (KTH Royal Institute of Technology), and Assoc. Prof. Matthias Bo Stuart (Technical University of Denmark DTU)

The presentation will highlight the structure and objectives of the project, including joint courses offered at the partner institutions, opportunities for student exchange, and the possibility of pursuing Master's thesis projects within the Edu4Chip framework.

|

From the 1st transistor, to FinFETs, and beyond

by Assoc. Prof. Flemming Stassen, Technical University of Denmark

This keynote will introduce the audience on a historical and technical journey through transistor evolution. Beginning with the pioneering transistor prototypes that launched the semiconductor revolution, the talk will present the architecture and scaling challenges of planar MOS devices. It will then transition to modern FinFET technology, unpacking its advantages in leakage control, performance, and scaling into the nanometer era. Finally, the presentation will explore newer and future approaches, such as gate-all-around transistors.

Flemming Stassen is an Associate Professor at Technical University of Denmark, where he carries out teaching in Digital Electronics, VLSI Design, and Test of Digital Systems. His long-standing teaching record and recognized excellence (DTU Faculty of the Year, 2001) reflect his passion for educating the next generation of chip designers. |

Design for low-power ICs for hearing instruments

by Evangelia Kasapaki and Vijay Kumar Bhat, from the company Demant

The keynote presents and discusses hardware strategies for supporting hearing instruments applications like audio processing, AI, and wireless communication on a constrained power budget.

Advanced hearing aids use integrated circuits (ICs) characterized by critical requirements of PPA: Power (power efficiency), Performance (throughput, latency, signal quality), and area (IC area, RAM, ROM, NVRAM). On the other hand, the hearing instruments need to handle diverse applications like audiology and wireless protocols. Thus, the hearing instruments ICs rely on high level of specialization in IC technology, digital-analog circuits, micro-controllers, DSP, and AI processors. Overall, the hearing instruments consist of multiple specialized ICs and within the ICs can be multiple processor cores, all these are tied together with performant yet efficient communication busses and NOC.

Evangelia Kasapaki and Vijay Kumar Bhat are industry experts working at Demant, a leading company in hearing aid technology. They have extensive experience in the design and development of low-power integrated circuits for hearing instruments. |

"Basic concepts in modeling" - A discussion of George Box's famous statement 'All models are wrong, some are useful' with a strong focus on models in chip design

by Prof. Dr.-Ing. Wolfgang Ecker, Infineon - Technical University of Munich

The keynote covers guiding principles of models and elaborates that the most important feature of a model is abstraction. It discusses different digital design abstraction methods — others say disciplines — as Lumped Model, Value Discrete Models and Time Discrete Models. It also relates these abstractions to pre-clustered elements as Transistors, Gates as well as Registers and Transfer Functions. The talk further discusses similarities between the abstraction levels and relates them to current IP-based design. All through the talk George Box’s famous statement is reflected. Situations and challenges are brought up, especially what happens if models are becoming reality.

Wolfgang Ecker is a Distinguished Engineer at Infineon and Professor at Technical University of Munich. His research and innovation focus lie on digital system modeling, digital design automation, SoC architectures, embedded AI and AI for design automation. He published over 200 papers, received six publication awards and has been granted with the German EDA achievement award. He is member of Acatech, the German Academy of Science and Engineering and has been member of the AI commission of inquiry of the German Government. |

Lectures

Chip design process overview

by Univ. Instuctor Arto Oinonen and Doctoral Researcher Matti Käyrä, Tampere University

This lecture provides an introductory overview of the chip design process, covering key steps from initial specification and architecture design to RTL development, verification, synthesis, physical design, fabrication, and final testing of the chip. The lecture covers also the design process including project management, scheduling as well as developer roles and expertise and overall resourcing. We use real System-on-Chip designs from sochub.fi as use cases and takeouts.

|

Agile hardware design in HDL

by Prof. Martin Schoeberl, Technical University of Denmark

The lecture on Agile hardware design with Chisel (Constructing Hardware in a Scala Embedded Language) focuses on using the Chisel hardware construction language as part of the agile hardware design process. Chisel is a modern hardware description language that enables designers to create digital circuits with concise, high-level code that is easier to write and maintain than traditional HDLs.

Agile hardware design applies modern software development methods to the design of hardware. With functional programming in Scala, you will learn how to write so-called hardware generators. This lecture includes hands-on describing a generator In Chisel. |

Systems-on-chip and interconnects

by Assoc. Prof. Luca Pezzarossa, Technical University of Denmark

This lecture provides an introduction to system-on-chip (SoC) architectures and interconnect technologies, essential for modern chip design. SoCs integrate multiple components such as processors, memories, accelerators, and peripherals into a single chip, enabling high-performance and energy-efficient computing. The lecture examines the challenges of designing scalable and flexible SoCs, focusing on SoC design principles and how different interconnect strategies (traditional bus-based communication, AXI4Lite, and advanced Networks-on-Chip (NoC) solutions) impact the design performance, power consumption, and modularity.

The lecture includes a hands-on laboratory session, where students explore the use of NoC based interconnect architectures in a multicore setting. |

Time-discrete analog circuits

by Dipl.-Ing. (Univ.) Markus Dietl, Technical University of Munich

The lecture covers the basics of time discrete circuits. Clocked analogue circuits are used very frequently in modern integrated circuit technology. There are inherently discrete-time circuits and those that convert an actually continuous variable (such as voltage) into a discrete-time variable by sampling, clocked charging or averaging.

Analogue-to-digital converters (ADCs) are an example of discrete-time circuits that convert the continuous variable of voltage into a discrete-time variable by sampling. DC-DC converters map a continuous voltage to another continuous voltage, but the conversion process utilises a clocked process. These converters therefore utilise a discrete-time control loop. Phase-locked loops (PLLs) generate frequencies and measure the time interval between two edges. They are therefore inherently discrete-time circuits. Both frequency and phase are discrete-time quantities. The lecture explains the difference to time continuous circuits, and how to model and design time discrete systems. |

Chip design process and challenges

by Assist. Prof. Ole Richter, Technical University of Denmark

In this lesson, we will walk through a small example of chip design, starting from a netlist to a real Application Specific Integrated Circuit (ASIC) design ready for fabrication. We will go through timing, placement, routing, and physical verification using publicly available tools. This presentation will give you a hands-on look at the potential challenges you may face in future projects and how to overcome them. We will examine the individual steps in timing, placement, routing, and physical verification and gain a deeper understanding of what is happening.

|

Verification of digital circuits

by Jacob Sander Andersen, from the company Syosil

This lecture, delivered by experts from Syosil, a Danish company specializing in verification solutions, covers the verification of digital circuits, focusing on methodologies and tools used to ensure design correctness (simulation, formal verification, etc.).

The lecture will cover some basic theory on functional verification and highlight some of the problems attached to the field, predominately explained through simulation based functional verification. A demo of formal verification will be given and lastly some small exercises involving constrained random verification will be conducted. |

Advanced topics: Asynchronous Circuits

by Emeritus Prof. Jens Sparsø, Technical University of Denmark

This lecture introduces asynchronous circuits, which are digital circuits that operate without a global clock. Unlike synchronous circuits, which rely on a central clock signal to coordinate operations, asynchronous circuits use local handshaking and data-driven control mechanisms. This class of circuits can lead to advantages in terms of power efficiency, performance, and robustness compared to traditional synchronous designs.

|

Advanced topics: Formal verification

by Prof. Oliver Keszöcze, Clausthal University of Technology

This lecture introduces hardware verification, comparing traditional testing with formal methods. We'll start by modeling digital circuits mathematically, laying the groundwork for understanding formal verification's rigorous approach. We'll explore how formal techniques, unlike testing, offer mathematical guarantees of correctness.

Building on that foundation, we will focus on the yopic of equivalence checking, which verifies that circuit designs are functionally identical. We'll discuss why this is a question of practical importance and learn methods for actually carrying out the equivalence test. |

Advanced topics: LEGO-inspired chip design

by Prof. Ahmed Hemani, KTH Royal Institute of Technology

Computer architects and the design automation community pursue efficiency improvements across multiple dimensions: computation, silicon, design, and manufacturing. However, state-of-the-art standard cell-based tooling has become unscalable, even as the demand for higher performance and computational efficiency continues to rise. To address these challenges, a Lego-inspired design framework called SiLago has been developed, demonstrating promising results—achieving 10 to 100 times better energy efficiency compared to COTS solutions. SiLago enables end-to-end automation while delivering ASIC-comparable efficiency. The generated designs are correct by construction, as well as timing and DRC-clean. Furthermore, SiLago is being explored beyond CMOS technologies, including applications in memristor-based computation and wave-based computing.

|

Other activities

-

Quickfire introduction of students

A fast-paced session where participants briefly introduce themselves to get to know each other. -

Student presentations (counts as the exam)

An interactive presentation session where students present their project outcomes, followed by an evaluation to conclude the summer school. -

Walking tour of Copenhagen (bring an umbrella!)

A tour to provide participants with an opportunity to explore the city’s vibe and architecture. Bus to Copenhagen departs at 16:10 from outside Building 101 (summer school location). -

Picnic on DTU premises

A welcome picnic on DTU premises. Location: Wicked Rabbit Kantine in Building 342. Google Maps link: View location -

Social dinner in Copenhagen

A social dinner in Copenhagen open to all the participants. Location: Restaurant Sult i Cinemateket, Vognmagergade 8B, 1120 København K. Google Maps link: View location

Learning objectives

A student who has successfully completed the summer school will be able to:

- Explain the fundamentals of semiconductor devices.

- Explain all steps in the chip design process.

- Apply principles of agile hardware design to describe and implement digital systems.

- Explain and analyze analog and mixed-signal design challenges.

- Explain and use simple verification tools to ensure proper hardware functionality.

- Describe the importance of sustainability for hardware designs.

- Compare asynchronous circuits with synchronous designs to evaluate their advantages and limitations.

- Illustrate the role and functionality of on-chip interconnects in modern chip architectures.

Student pre-registration

Participation in the Edu4Chip Summer School is free of charge for students. However, due to limited capacity, we require all interested student participants to pre-register. This process helps us ensure a diverse and balanced group of students from different institutions and backgrounds.

To pre-register, please complete the Pre-registration by March 31th, 2025. After reviewing all applications, selected participants will receive a confirmation of admission via email and you will be prompted to the registration portal.

Important Information:

- Pre-Registration deadline: March 31th, 2025

- Student participation fee: Free of charge

- What is included: All lectures, keynotes, program materials, snacks, and lunches.

- Not included: Travel, accommodation, private expenses, and social activities (optional), which must be covered by participants.

For those in need of financial support for the expenses that are not included, please refer to the Financial support section for information on available funding options. Please note that the deadline for applying for financial support depends on the institution you are from and might be earlier than the pre-registration deadline (see the Financial support section).

Student financial support

To support student participation in the Edu4Chip Summer School from countries outside Denmark, two financial support options are availble to help cover travel and accommodation costs.

Support via Erasmus+ Blended Intensive Program (BIP)

The support via Erasmus+ Blended Intensive Program (BIP) is available to students from any DTU Erasmus+ partner institutions. This support helps cover travel, accommodation, and other expenses for eligible participants.

Eligibility: Students enrolled at DTU Erasmus+ partner institutions. In the context of Edu4Chip, these are KTH Royal Institute of Technology, Technical University of Munich (TUM), and Tampere University (Finland). However, students from other institutions that are Erasmus+ partners of DTU might be eligible for this support. Please contact your institution's international/Erasmus office for application details and procedures.

Support via Edu4Chip

The Edu4Chip project can provides financial support for students from Edu4Chip partner institutions to cover travel, accommodation, and other expenses related to the participation in the summer school.

Eligibility: Students from all Edu4Chip partner universities .

More information and applications

If you are from one of the Edu4Chip partners, see the contact person in your institution below. If you are from another university, you might still be eligible for support via Erasmus+ Blended Intensive Program (BIP), if your institution is an Erasmus+ partner of DTU. Please contact your institution's international/Erasmus office for application details and procedures.

For students from the Technical University of Munich (TUM):

|

Contact person: PD Dr.-Ing. habil. Michael Pehl Mail: m.pehl@tum.de Phone: +49 (89) 289 - 28252 Homepage: Link to homepage |

For students from KTH Royal Institute of Technology:

|

Contact person: Prof. Ahmed Hemani Mail: hemani@kth.se Phone: +46 8 790 44 69 Homepage: Link to homepage |

For students from Tampere University (TAU):

|

Contact person: Prof. Timo Hämäläinen Mail: timo.hamalainen@tuni.fi Phone: +35 8408490777 Homepage: Link to homepage |

For students from Institut Mines-Télécom (IMT):

|

Contact person: Prof. Jean-Max Dutertre Mail: dutertre@emse.fr Phone: +33 (0)4 42 61 67 36 Homepage: Link to homepage |

For students from the Technical University of Denmark (DTU):

|

Contact person: Assoc. Prof. Luca Pezzarossa Mail: lpez@dtu.dk Homepage: Link to homepage |

We encourage all interested students to apply early to secure funding support.

Other information

DTU's 3-week special course

For DTU students only, we plan to integrate the summer school into a DTU 3-week special course worth 5 ECTS, which includes an additional project week to further develop and apply the concepts learned. The course reposnible will be Luca Pezzarossa and the course will be structured as follows.

Week 1: Preparation & project selection (August 11-15)

- Participation in the Summer School Intro-Day (August 11th).

- Background review on key topics covered in the summer school.

- Introduction to project options and selection of practical projects.

Week 2: Edu4Chip Summer School (August 18-22)

- Intensive lectures, presentations, and hands-on activities.

- Keynotes and industry insights.

- Networking and social events.

Week 3: Practical project execution (August 25-29)

- Work on the selected projects, with guidance from the teacher.

- Application of design, verification, and testing methodologies from the summer school.

- Exploration of one or more key topics in greater depth.

- Final report and/or presentation to summarize findings and outcomes.

Learning Objectives

The learning objectives of the special course are aligned with those of the summer school (see above).

Questions and contacts

If you have any questions about the Edu4Chip Summer School, feel free to reach out to us. Whether you need more information about the program, registration process, participation grants, or logistics, we are here to help!

|

Contact person: Assoc. Prof. Luca Pezzarossa Mail: lpez@dtu.dk Homepage: Link to homepage |