# Joint Education for Advanced Chip Design in Europe (Edu4Chip)

**Deliverable Report**

# **Curriculum of Master Programs and Specializations** in Edu4Chip

| Author(s)            | Michael Pehl (TUM), Luca Pezzarossa (DTU), Matthias Bo Stuart (DTU),<br>Jean-Max Dutertre (IMT), Ahmed Hemani (KTH), Arto Oinonen (TAU),<br>Hussam Amrouch (TUM) |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date:                | March 28, 2025                                                                                                                                                   |

| Version:             | 1.0                                                                                                                                                              |

| Due Date:            | March 31, 2025                                                                                                                                                   |

| Dissemination Level: | Public                                                                                                                                                           |

| Work Package No:     | 2                                                                                                                                                                |

| Deliverable Number:  | D2.2                                                                                                                                                             |

| Lead Beneficiary:    | TUM                                                                                                                                                              |

**Disclaimer:** Funded by the European Union. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union or European Health and Digital Executive Agency (HADEA). Neither the European Union nor the granting authority can be held responsible for them.

| Abstract                                                                               | 4 |

|----------------------------------------------------------------------------------------|---|

| Chapter 1. Goal of Study Programmes                                                    | 5 |

| Knowledge and Understanding                                                            | 5 |

| Skills and Abilities                                                                   | ô |

| Communication Skills                                                                   | ô |

| Scientific Self-Concept                                                                | 7 |

| Chapter 2. Target Group                                                                | 3 |

| Addressed Audience                                                                     | 3 |

| Expected Previous Knowledge                                                            | 3 |

| Chapter 3. Common Structure of Master Programs and Study Directions                    | Э |

| Chapter 4: Competence-Based Explanation of the Aligned Programmes                      | C |

| Theoretical and Methodological Base-Competence and Expertise                           | C |

| Basic and Expert Competences in Practical Chip Design1                                 | 1 |

| Communication and Research Skills1                                                     | 3 |

| Interdisciplinary Qualifications1                                                      | 3 |

| Internationality, Mobility, Digitization14                                             | 4 |

| Final Academic Project14                                                               | 4 |

| Chapter 5. Structure of the Study Programs and Study Directions by University Partners | 5 |

| Technical University of Denmark (DTU)1                                                 | 5 |

| Program Structure and Requirements1                                                    | 5 |

| Relation between Courses and Competences10                                             | 6 |

| Institut Mines-Télécom (IMT) – École des Mines de Saint-Étienne                        | 7 |

| Programme Structure at ISMIN Curriculum1                                               | 7 |

| Relation between Structure and Competencies at ISMIN                                   | 9 |

| Programme Structure at MS CCM Curriculum19                                             | 9 |

| Relation between Structure and Competencies at MS CCM                                  | C |

| KTH Royal Institute of Technology (KTH)2                                               | 1 |

| Formal Structure                                                                       | 1 |

| Relation between Structure and Competences                                             | 2 |

| Tampere University (TAU)                                                               | 3 |

| Program Structure and Requirements 23                                                  | 3 |

| Relation between Courses and Competences24                                             | 4 |

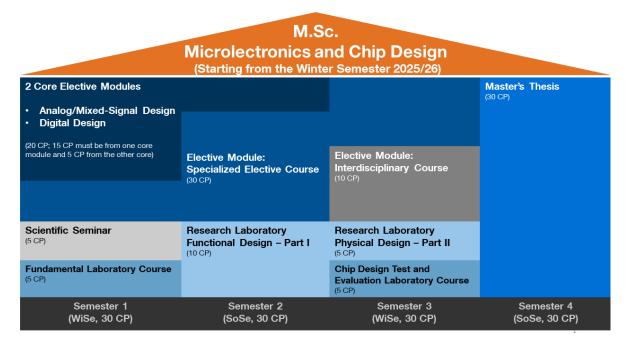

| Technical University of Munich (TUM)                                                   | 5 |

| Formal Structure                                                                       | 5 |

| Relation between Structure and Competences                                             | 6 |

| Chapter 6. Course Catalog for Lifelong Learning                                        | 9 |

| DTU, Catalog and brief description of Lifelong Learning courses                        |   |

| Agile hardware design with the Chisel HDL language (1 - 2 days)                        |   |

| Chip design using open-source tools (1 - 2 days)                                       |   |

| IMT, Catalog and brief description of Lifelong Learning courses                            |

|--------------------------------------------------------------------------------------------|

| Hardware Security training, Theory and Practice of Fault Injection Attacks (10h)           |

| Hardware Security training, Theory and Practice of Side Channel Analysis attacks (10h)     |

| Digital Design training, FPGA design flow (21h, 3 days)                                    |

| IC Manufacturing training, Fabrication of a MOS capacitor in a clean room (21h, 3 days) 31 |

| TAU, Lifelong Learning course                                                              |

| System-on-Chip Verification (5 Credits, 14 Weeks)                                          |

| TUM, Lifelong Learning course                                                              |

| AI Chip Design: From Fundamentals to Industry Applications                                 |

| Chapter 7. Summary                                                                         |

| Appendix A: Lists of Main Courses Offered by Participating Universities                    |

| A.1 Preliminary Course List of TUM                                                         |

| A.1.1 TUM - Core Elective Modules Analog/Mixed-Signal Design                               |

| A.1.2 TUM - Core Elective Modules Digital Design                                           |

| A.1.3 TUM - Elective Courses                                                               |

| A.1.4 Practical Chip-Design Modules                                                        |

| Fundamental Laboratory Course                                                              |

| Research Laboratory Functional Design - Part I                                             |

| Research Laboratory Physical Design - Part II                                              |

| Test and Evaluation Laboratory Course35                                                    |

| A.2 Course List of DTU                                                                     |

| A.3 Course List of IMT                                                                     |

| A.4 Course List of TAU                                                                     |

| A.5 Course List of KTH                                                                     |

# Abstract

The Edu4Chip partner universities – the Technical University of Denmark, the KTH Royal Institute of Technology, the École des mines de Saint-Étienne of IMT, the Tampere University, and the Technical University of Munich – aim to setup aligned Master programmes and specialization directions in the domain of chip design. This effort is funded by the European Union through the program Edu4Chip. This document summarizes the curriculum of the university partners and provides an overview of the programmes' goals, teaching strategies, and planned implementation. Some new or significantly improved courses for the programmes have been already started in existing study direction in a first version. The complete programmes at the different universities will start in summer and fall 2025.

# Chapter 1. Goal of Study Programmes

Chip design deals with the development of complex systems as integrated circuits. The past has shown that bottlenecks in the international supply chains can lead to a significant burden on the economy in Europe so that Europe must reduce its dependence on non-European markets. To this end, Europe want to strengthen the ability to develop and manufacture chips in Europe. A significant number of highly qualified workers with the ability to solve current tasks in the field of chip design and to develop innovative solutions is required.

The aim of the Master's degree programs and specializations at the universities participating in the Edu4Chip project is to train highly qualified, innovative and responsible engineers who can develop and implement new specialized, technologically high-quality solutions in the field of microelectronics in the form of chip designs, such as those required in the field of artificial intelligence, information security or in the development of energy-saving systems. In their role, graduates should be able to implement important analog and mixed-signal components, such as sensors or digital-to-analog or analog-to-digital interfaces, or implement complex digital systems, such as processors including accelerators for specialized applications, in hardware. Graduates from the programs and specialization directions will take on tasks along the entire design process of circuits. This includes activities as system designers, development engineers. By specializing in areas such as design for artificial intelligence or information security, students are not only able to find generic solutions, but can also develop tailor-made solutions for their field of specialization that go beyond the state of the art. This also enables graduates to make a contribution to university research.

The degree programmes and specialization areas are highly application-oriented and at the same time includes significant research-oriented components. They enable students to carry out activities in the field of application-oriented research as well as in the development of innovative solutions for companies and industry. In particular, students will comply with the following requirements of their qualification profile.

### Knowledge and Understanding

Graduates of the Master's programs and specialization directions developed in Edu4Chip are able to independently develop complex systems, which are often required to solve future-oriented technological solutions, in the form of integrated circuits and the associated hardware-related software. They are able to analyze, test and further develop existing and newly developed systems. In particular, the graduates have a deep understanding of all the work steps that have to be carried out in the development of a complex microelectronic chip, starting from an abstract description to physically existing hardware. Thus, they are able to apply their knowledge to new, previously unknown problems.

Building on the fundamentals of Bachelor's degree programs in domains like electrical engineering, computer science or physics, graduates are able to understand the physical principles (e.g., the relationships between technology, circuit design, and timing or power consumption) that play a role in chip design. This includes a comprehensive understanding of electronic and solid-state theoretical effects, which play a role in the finished chip and in modern circuit manufacturing technologies. Graduates are able to model and partition complex systems for circuit development algorithmically or mathematically and to convert the modeling into a form suitable for hardware development. They can transfer these models into efficient implementations based on their knowledge. They understand the

mathematical methods (e.g. graph theoretical, statistical or numerical approaches and their links) that are used in chip design tools, e.g., for optimizing circuits, or for placement and routing, and can use the tools in a targeted manner.

#### **Skills and Abilities**

In addition to the indispensable specialist knowledge in the circuit design domain, graduates also have collaborative skills, perspectives and agile working methods for the new world of work (21st Century Skills) across the boundaries of disciplines. A focus is also placed on the topic of sustainability, which in the context of chip design can be done primarily through the implementation of low-energy concepts.

Graduates are able to successfully work on complex problems and issues in the area of chip design based on their specialist and methodological knowledge. They are able to transfer domain knowledge to an application area (e.g. robotics or medical systems) through a deep knowledge of the basic methods of circuit design and the physical and mathematical relationships they understand. This ability is learned through practical lab courses where they apply theoretical concepts of circuit design to concrete design tasks. Graduates from the program are able to critically question the state of the art and thus identify weak points, which in turn can lead to new research questions and innovative solutions. In addition, they can assess the impact of their decisions w.r.t. economy, ecology, and society. Graduates can also recognize the research needs that arise, for example, from the introduction of new technologies and can plan steps for conducting research and to carry out scientific experiments.

During their later career, graduates can use the methods they have learned to develop and implement new innovative ideas. In particular, the practical aspects of chip design allow graduates to implement even complex projects independently. The acquired competence in project-oriented cooperation with third parties in conjunction with a sound methodological knowledge allows students to contribute their competence to interdisciplinary teams and in this way to develop innovations beyond known application domains.

## **Communication Skills**

Students in the Master's programs and specialization areas in Chip Design have excellent teamwork skills. They are able to plan and carry out projects independently, will be familiar with the structure and dynamics of group situations, and will be able to divide tasks within a working group according to individual competences. They are able to recognize group conflicts at an early stage and develop solution strategies. Due to the international character of the programmes and the cooperation with other universities, graduates are also able to act confidently in other cultures and to work constructively with international colleagues.

Graduates also have knowledge from the interdisciplinary field, which allows them to act in a wellfounded and situation-appropriate manner in addition to the technical aspects with regard to ecological and economic concerns. Their training also allows them to communicate confidently scientifically, but also non-scientifically, in speech and writing, tailored to a target group.

# Scientific Self-Concept

Graduates of the Chip Design programmes have strong technical knowledge that enables them to make scientifically and technically sound decisions. A high degree of practical skills allows them to assess the feasibility of projects realistically and in relation to their individual abilities and skills of their working group. They have in-depth experience in group-oriented and project-related work in an intercultural context. All this knowledge and skills shape their scientific and professional self-concept. Graduates proceed methodically in new scientific and technical tasks on the basis of the skills they have learned, while responsibly keeping an eye on the overall situation and the consequences of their actions. They question their actions critically and self-reflectively and are able to act prudently and ecologically, economically, and socially responsible, even in conflict situations. In particular, they are able to assess the ethical and ecological opportunities and risks of the technologies they have co-developed in a comprehensible manner and to make appropriate socially responsible decisions, for example with regard to the further pursuit of ideas or the use of technologies. With these skills, graduates are able to take on tasks in industry but also scientific activities at universities and research institutions. Their knowledge enables them to act innovatively and responsibly in these environments.

# Chapter 2. Target Group

#### Addressed Audience

The Master's degree programs and specialization directions in Chip Design target mainly graduates from Bachelor programs in the fields of electrical engineering, computer science, and physics in Europe. The requirements may also be met by Bachelor's graduates from other international universities, colleges, dual universities and equivalent institutions.

The programmes are aimed at applicants who are interested in contributing to innovative future solutions through the development of analog/mixed-signal or digital circuits in modern technologies. The degree programmes offer applicants the opportunity to work on a chip design as part of their studies and to create their own design. They have the opportunity to develop an innovative design by, for example, participating in the development of hardware accelerators for artificial intelligence or security.

Since all courses of the degree programmes are held in English<sup>1</sup> and the degree program also focuses in particular on the labor requirements of internationally active companies in the field of chip design, it is not only aimed at applicants from the environment of the Edu4Chip partner universities, but also to a large extent applicants from international countries, whereby within the framework of EU funding for the development of the degree programme, the training of students from European countries is to be strengthened in particular.

# **Expected Previous Knowledge**

In order to achieve the desired qualification goals in the Chip Design degree programmes, first-year students are required to have initial qualifications. On the one hand, this includes sound mathematical skills as taught in all technical and scientific degree programs at the partner universities. Examples are extensive previous knowledge in the areas of numerics and statistics. On the other hand, it is required that applicants have a good knowledge of essential electrical engineering relationships. Learned content from the field of digital technology and computer architectures can serve as examples of this previous knowledge as well as a good understanding of electrodynamics. In addition to the technical/scientific and mathematical skills mentioned above, applicants should also have basic programming skills in order to get familiar with required skills regarding scripting languages and description languages required in the course of the study programmes – especially in the practical parts of tool operation – with low effort. Since the program is also offered to international students and is taught in English (cf. footnote 1), applicants must also have good English language skills.

<sup>&</sup>lt;sup>1</sup> As an exception, several courses at the partner university L'École des mines de Saint-Étienne will be provided in French and students might have the degree of freedom to select additional courses in another language at all partner universities.

# Chapter 3. Common Structure of Master Programs and Study Directions

The following description is mostly taken from the previous concept document of Edu4Chip (Deliverable D2.1, "The Program Concept"). More details can be found there.

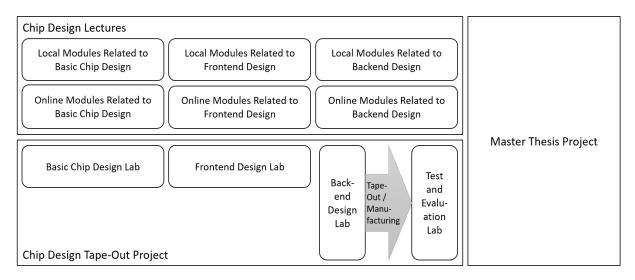

The overall structure of the study program is shown in Fig. 1. It is a four-semester program with one semester reserved for the preparation of a Master thesis.<sup>2</sup> Two semesters constitute one study year. The workload per semester is usually 25 to 35 ECTS credits. The total number of credits is 120 credits (incl. Master thesis). The instruction language of the program is English (cf. footnote 1).

The precise implementation of the program and the degree to which students are enforced to follow the program varies between partners due to local regulations. From the basic idea, however, the first semester focuses on basic skills in digital and analog design. The second semester includes more advance topics related in particular to the front-end design. For the third semester, the program offers further specialized courses and courses related to the back-end design. The overall program consists of a more theoretical part with lectures from the domain of chip design and a practical part in which students will do a tape-out. A Master thesis will conclude the study program, which can also be conducted in collaboration with industry.

The Master programs are aligned between university partners, to make exchange of students easy. For this purpose, an exchange window is foreseen in the study programs.

<sup>&</sup>lt;sup>2</sup> The partner university L'École des mines de Saint-Étienne fomally has no Master thesis. Students at this university have to complete a one-semester intership in a company or at a research team and write an internship report that is close to what is expected from a Master Thesis.

# Chapter 4: Competence-Based Explanation of the Aligned Programmes

This chapter outlines which competences should be received by students specializing in chip design through a corresponding Master program or specialization direction. Not all skills in the wide area of chip design are taught at all partner universities of the Edu4Chip project due to different local requirements and expertise. However, the alignment of the programmes between the partners allows students to take courses from another university, e.g., during an exchange semester. The diverse focus areas of each university help offer a broader selection of courses, giving students access to a more diverse and comprehensive and up-to-date learning experience.

Overall, the competences required for chip design can be subdivided in the following parts:

# Theoretical and Methodological Base-Competence and Expertise

Students should be able to take on tasks in the field of chip design, in particular either with a focus on analogue/mixed signal design or with a focus on digital design. This requires certain dedicated qualifications. The basic qualification profile includes an advanced understanding of the physical relationships and functionality of integrated circuits and a good understanding of the functionality of design tools and optimization algorithms and methods used in these tools. In addition, the capability to apply the knowledge regarding integrated circuits and design tools to design new integrated circuits is needed. The skills required for digital designers and analogue/mixed signal designers differ here; for example, significantly larger circuits are developed in the digital field, which can only be handled practically at high levels of abstraction, while analogue design involves working at a low level of abstraction with few transistors. In order to take this into account, different specialization directions are offered by the Edu4Chip partners based on the local expertise. In order to achieve the goal of specializing in the analogue/mixed-signal area or in the digital area, skills for the respective area that go beyond a Bachelor's degree are taught. Depending on the choice, this can be, for example, competencies/skills in the digital area with regard to the optimal division of algorithms into hardware and software components or with regard to the testing of digital circuits and the development of digital circuits taking into account their analogue behavior. In the analogue/mixed-signal area, the skills include, for example, the development of specialized analogue circuits or so-called standard cells for digital circuit design. In order to enable the necessary collaboration of designers in their later professional life, it is not enough for students to acquire only basic skills in their specialization. Students specializing in digital design must also be able to understand up to a certain extend analogue components; students specializing in analogue/mixed-signal design must be able to develop new circuits in the context of predominantly digital systems and integrate the analogue circuits they have developed into a complex digital circuit. The different prior knowledge of students from different Bachelor's degree programmes is taken into account in the Master programs by offering a choice within the modules targeting basic qualification. The courses targeting basic knowledge shall be taken early in the studies, to provide the necessary knowledge for courses that build on this background.

Based on these courses, students are given the opportunity to specialize in one or more area(s) of chip design. For example, they can focus on highly relevant topics such as design of secure hardware, design of hardware accelerators for AI or design of integrated high-frequency circuits. These topics are not only important for industrial applications but have also significant relevance in research and impart

sophisticated specialist knowledge and skills with the aim of preparing students for both industrial work and research activities following the Master's programme. As part of the technical in-depth study, the topic of sustainability is considered.

The selection of subject-specific specializations is open to students. Modules offered are usually provided rather in form of lectures and focus on theoretical concepts and methods, mostly with a clear link to applications; the link to applications might also come through exercises, homework or practical courses. Lecturers from industry are involved in teaching at this point, which creates very good link practice. Specialized competencies might also be broadened during stays abroad at the partner universities or by taking selected modules from programs like the EuroTeQ course program (there, e.g., modules on Microprocessors or Biomedical Microelectromechanical Systems are offered).

## Basic and Expert Competences in Practical Chip Design

Qualification as a chip designer requires the ability to implement theoretical concepts practically and to achieve high quality circuit designs. As a base for this, students must learn to abstract theoretical concepts and algorithms and to convert them into a hardware description. Students may take a basic practical course in the programmes of the partner universities that prepares students for this task either in the field of digital or analogue circuit design. Students specializing in digital circuit design need to acquire very good knowledge of a hardware description language and the conceptual procedure for describing certain hardware components correctly and efficiently using such a language. They also need to learn essential strategies for simulating and testing digital systems at different levels of abstraction. Students with a focus on analogue circuit design need to learn to independently design basic analogue circuits at transistor level and determine and test the key characteristics of such circuits using simulation.

In order to gain expertise in the development of high-quality, innovative chips, it is necessary for students to come into contact with typical practical issues and difficulties in the practical realization of a chip in selected application areas/domains and gain corresponding experience. An example of such a problem from the field digital chip design is the design of an accelerator for an AI application under constraints regarding the permissible area, frequency, and latency. Such a design task requires considerations regarding the division into hardware and software components and a high-quality implementation of these components in order to achieve the best possible result. In the programmes developed in Edu4Chip, the teaching of this competence is realized by project-oriented laboratory courses. In these, students go through the process of chip design from a specification to the implementation of a design that results in a tape-out ready chip that shall also be manufactured. In a subsequent laboratory course, the students bring up the chip, test it, and evaluate their results.

To design and fabricate chips, students need access to chip design software tools, a Process Design Kit (PDK) that describes the target technology, and standard-cell libraries for implementation. These are essential components for creating functional designs and preparing them for fabrication. However, the use of these components is subject to legal constraints. Commercial PDKs often require students to be included in non-disclosure agreements (NDAs), which cannot be enforced as a condition for mandatory courses. Therefore, to ensure compliance with legal requirements and offer equal opportunities to all students, two options are considered: commercial and open-source.

The first option is based on commercial tools, PDKs, and standard cells. The tools and standard-cells, such as those provided by Cadence and Synopsys, are widely used in the industry and made available to universities through Europractice for teaching and research purposes. Chip fabrication in commercial technology is typically done using PDKs and standard cells from foundries such as

GlobalFoundries (GF), STMicroelectronics (ST), Taiwan Semiconductor Manufacturing Company Limited (TSMC), or United Microelectronics Corporation (UMC). While this option provides students with industry-relevant experience, it also requires the use of licensed and NDA-covered PDKs for access to the technology.

The second option is open-source tools and fabrication. In this case, students will have the opportunity to work with open-source tools, such as OpenLane, as well as open-source PDKs and standard-cells, such as those offered by the Leibnitz Institute for Innovative Microelectronics (IHP) or Skywater Technology. This track does not require NDAs, and in certain cases, students can still fabricate chips using open-source technology. While the open-source approach provides valuable insights into chip fabrication, students may not encounter some of the same challenges present in commercial technologies.

Each partner university will use either one or both of commercial and open-source tools and PDKs. The decision to use one or both options may be directed by local regulations. This diversity enriches the Edu4Chip program by offering students the opportunity to experience both open-source and commercial design environments, providing a more comprehensive understanding of the different approaches and challenges in chip design and fabrication.

The laboratory courses to gain expertise in practical chip design is based on the basic practical knowledge described above. The design part in it is provided in two parts: In the first part, students with a focus on digital circuit design work on the functional digital design. They have to implement an algorithm from a specific application domain. Basic strategies of hardware/software co-design must be taken into account, as well as specifications regarding, for example, area, clock frequency or power consumption. Depending on the university, students may be able to choose one of several fields of application, such as hardware design for security or acceleration of AI. Working in groups, the students then develop a concept based on the specification provided, including a work plan for implementation and a verification plan. The concept as well as the work and verification plan are presented, discussed and improved together with supervisors. The concept is then implemented and the design is synthesized into a gate-level netlist; the skills learned in the basic practical course are used here. Successful completion of the practical course is demonstrated by means of project work, in particular by tests that prove the functional correctness of the circuit and compliance with specifications. After completing the first part, the students continue in the second part with a practical course on the physical design of digital circuits. I.e., the students go through the steps from a gate-level netlist to the generation of mask data that can be sent to a chip factory. In particular, acquired knowledge of the algorithms used in the design tools and an understanding of the analogue behavior of digital circuits are deepened in this part. Successful completion of the practical course is demonstrated by the presentation of a design that takes into account all design rules that must be observed for chip production and that passes an equivalence test of the design before and after the various work steps have been carried out.

Students with a focus on analogue circuit design follow a structurally similar path. The main differences here are the specification and the start and end points of the various work steps. The task given to such students consists of the specification of circuit properties for an analogue component, such as for a phase-locked loop, based on which they have to realize the functional design of an analogue/mixed-signal circuits. This component is developed in the first part of the practical course where they realize their design on transistor level and test it using simulation. In the subsequent second lab part on physical design of analogue/mixed-signal circuits, the layout of the design is developed by the students. Proof of passing the course is equivalently defined to that for students in the digital domain.

In order to ensure that the task in the area of circuit design is feasible in terms of complexity and that the chips produced are functional, the tasks described are development tasks for sub-components of a design that are to be integrated into a template chip with housekeeping functionality. The practical courses on the functional and physical design of circuits should be taken as described above due to the logical connections in the design process, so that the students in the two labs develop a chip in a group from specification to tape-out. For practical reasons, the parts of the laboratory course are decoupled to extent the flexibility, e.g., for students that cannot take part in both parts due to urgent personal reasons.

The two-part laboratory courses in chip design and the test and evaluation laboratory course are designed in such a way that at least at some Edu4Chip partner universities individual students can also contribute their own project ideas or the laboratory courses can be carried out with industry partners. If students propose such projects, they must find a professor involved in the Master's programme, that confirms the feasibility of the project and its equivalence to the specified projects, and takes the role of examiner or supervisor as per local regulations.

#### Communication and Research Skills

Today's chip design engineers do not only need the technical knowledge to realize a circuit hardware. They also need to be able to discuss possible solutions, work in groups, and carry out, e.g., literature research and have thus capabilities that are not only relevant in industry but also for a career in research. Such competences can be learned in a master program in different ways: As part of the chip design labs above, students will work in groups to develop a given specification to the final chip. They will have to present, to discuss, and to defend their concepts and results, e.g., in seminars. In order for students to be able to work independently seminars teaching students how to carry out complex research work are provided at some of the partner universities. In addition, to possible seminars, supervision during the chip design project is used to support students in learning or to explicitly teach students in how to reasonably structure, organize, and perform project and group works.

#### Interdisciplinary Qualifications

As explained above, students in the Edu4Chip programs are trained in communication skills through the group-based chip design lab and potential seminars. In addition, students can acquire interdisciplinary skills within their master studies. This comprises subject areas such as ecology or sustainability, which specifically trains a sense of social responsibility. In addition to such sociological topics, lectures from application domains such as automotive, avionics or medical technology might be selected by students in order to build up knowledge in additional application domains and to enable them to apply their chip design expertise to such a field. It should be noted here that all students may already come into close contact with selected application areas/domains in the chip design project (e.g. topics such as AI or security), as they have to develop a chip in a specific application domain. The choice from additional application domains supports in particular an understanding of the requirements for chip design that will later be placed on graduates, supports the development of interdisciplinary communication as well as critical, fact-based reflection and argumentation by students.

#### Internationality, Mobility, Digitization

Most of the programs and specialization directions are provided in English language (an exception are the programs developed at IMT, where the programs will be taught in French language due to local requirements). Thus, they inherently address international students from European and non-European countries. This aspect alone leads to a cosmopolitan culture in the programmes and a high level of internationality through cooperation in international project groups. In additional exchange places within the framework of the Erasmus+ programme between the European universities participating in Edu4Chip are under conclusion or have already been concluded. As the chip design programmes offered at the partner universities are aligned with each other, the partner universities can determine which lectures will be recognized and in what form; this information will then be made known to all students, for example via the course website, so that students can easily decide which university in the consortium is a good target for the individual wishes regarding an exchange. This will make it much easier to study abroad. For some university partners it is planned to offer selected courses remotely so that students from another university involved in the Edu4Chip project can participate. It has to be noted, that due to significant legal and administrative obstacles this will only be possible within the framework of existing/other frameworks such as the EuroTeQ Engineering University. The EuroTeQ Engineering University project already offers a way to facilitate a digital exchange programme, at least between TUM and DTU. Some of the participating universities have foreseen a designated exchange window for students in the Master's programme; This shows students an optimal time slot to spend time at other universities abroad.

In addition to the direct exchange measures in the degree programme, the summer schools planned for the Edu4Chip project, in which students from the Master's programmes as well as students from upstream Bachelor's programmes are to be given the opportunity to come into contact with current topics in the field of chip design, represent a further opportunity for internationalization.

#### **Final Academic Project**

All master programmes comprise a Master's thesis is the final academic project (cf. footnote 2), usually in the last semester. As part of the Master's thesis, students must solve a specific, complex problem in the field of the study direction by independently designing and carrying out a practical research project either in industry or at a university. The theoretical and practical approaches and scientific methods learned during the course are applied. The Master's thesis has the character of a project work, in which not only practical activities are required, but also planning and conceptual components are included, which correspond to the comprehensive range of tasks in professional life or the work of engineers in chip design.

# Chapter 5. Structure of the Study Programs and Study Directions by University Partners

This chapter details the specific implementation of the programs at the different universities and links the structure of the programs to the expected competences above.

# Technical University of Denmark (DTU)

DTU integrates the Edu4Chip initiative into its existing MSc program in Computer Science and Engineering, primarily within the Digital Systems specialization. The integration involves adapting selected existing courses to include Edu4Chip activities and developing new courses. While the Digital Systems specialization is the main focus, any student enrolled in the MSc Computer Science and Engineering program can take Edu4Chip courses, regardless of their chosen specialization. At DTU, specializations are considered suggestions rather than mandatory pathways, allowing students to tailor their studies according to their interests and career goals.

#### **Program Structure and Requirements**

To obtain the MSc degree in Computer Science and Engineering, students must complete 120 ECTS credits, which are distributed as follows:

- 1. Polytechnic foundation courses (minimum of 10 credits)

- 2. Program-specific courses in computer science and engineering (minimum of 50 credits)

- 3. Master's thesis project (30 credits)

The remaining credits can be earned through elective courses, allowing students to tailor their academic journey to their specific interests. The Edu4Chip courses can be selected as part of the program-specific courses or the elective component. Within the Digital Systems specialization, students are encouraged to follow a selection of courses (reported below), which spans the entire duration of the program and include the chip design project. While these courses are highly recommended for students interested in chip design, these are not mandatory due to regulations.

The courses integrated into the Edu4Chip initiative include both existing and newly developed courses. These courses ensure that students gain both theoretical knowledge and practical experience in designing, implementing, verifying, and testing digital systems. The key Edu4Chip courses at DTU are:

- 02118 Introduction to Chip Design (5 credits)

- 02155 Computer Architecture and Engineering (5 credits)

- 02203 Design of Digital Systems (5 credits)

- 02201 Agile Hardware Design (5 credits)

- 02205 VLSI Design (5 credits)

- 02207 Verification of Digital Systems (5 credits)

- 02209 Test of Digital Systems (5 credits)

- 02211 Research Topics in Computer Architecture (5 credits)

- 02214 Hardware/software codesign (5 credits)

In addition to these standard courses, special courses can be requested by students. Special courses are custom-designed, research-oriented courses created on demand to allow students to deepen the learning of the provided topics or explore advanced and emerging topics in close collaboration with

faculty. Within the Edu4Chip initiative, students can leverage special courses to further work on the chip design project. Moreover, these courses can also serve as a preparation for the Master's Thesis, allowing students to engage in deeper research and refine the technical foundation required for their thesis work

#### **Relation between Courses and Competences**

To ensure a comprehensive foundation in digital design and computer architecture, students are encouraged to take key course 02203 – Design of Digital Systems, which introduces RTL-level design and advanced hardware implementation. This is complemented by 02155 – Computer Architecture and Engineering, where students gain a deeper understanding of processor design, memory hierarchies, hardware-software interaction, and performance optimization.

More advanced angles to digital design and computer architecture are provided by 02201 – Agile Hardware Design, 02211 – Research Topics in Computer Architecture, and 02214 – Hardware/software codesign. 02201 – Agile Hardware Design introduces modern techniques in Chisel-based hardware design, emphasizing circuit generation, object-oriented hardware modelling, and test-driven development. 02211 – Research Topics in Computer Architecture covers advanced concepts in network-on-chip architectures, time-predictable systems, and AI accelerators. 02214 – Hardware/software codesign teaches design processes to partition systems in hardware and software components according to given requirements and to codesign all system components for faster development times.

The chip design back end is covered by 02118 – Introduction to Chip Design and 02205 – VLSI Design, each offering complementary content. 02118 – Introduction to Chip Design focuses on open-source tools and design flows. The course includes virtual and physical tape-out experiences, such as those using OpenLane and the Skywater PDK/standard-cells, as well as Tiny Tapeout. 02205 – VLSI Design emphasizes the use of commercial design tools and covers MOS technology, ASIC and SoC design flows, along with timing, power optimization, and low-power design techniques. This course is a more advance course providing a solid theoretical understanding as well as allowing students to interact with the commercial industry-standard back-end design tools.

Competencies in design verification and testing are covered by 02207 – Verification of Digital Systems and 02209 – Test of Digital Systems. These courses focus on testbench creation, constrained-random verification, fault modeling, design-for-test (DFT) strategies, etc. equipping students with the necessary tools to ensure the functional correctness and reliability of complex digital designs.

Practical experience is a central element of the program, where all courses incorporating a hands-on project. Together, these course projects contribute to the multi-semester chip design project. This integrated approach ensures that students develop a cohesive understanding of the chip design process. For those seeking deeper specialization, special courses may be utilized.

The final semester of the MSc program is dedicated to the Master's Thesis Project (30 credits). The thesis is typically an individual or group project that allows students to apply the knowledge and skills acquired throughout the program to solve a practical or research problem. Students have the option to collaborate with DTU research groups or pursue their thesis in partnership with industry. The thesis may focus on a broad range of topics. Expected topics include digital circuit design, verification methodologies, high-performance designs, system-on-Chip architecture and accelerators, real-time and safety critical systems, open-source tools for chip design.

Students who have participated in the chip design project are encouraged to extend their project into a full thesis. In this case, the thesis can focus on refining, extending and testing the design, or applying the learned chip design methodologies to new application domains.

The flexible nature of DTU's MSc program encourages students to engage in interdisciplinary learning through elective courses. These electives can cover a broad range of topics, including robotics, green energy, and medical technology. These topics are not directly integrated into the Digital system specialization, but student are encouraged to explore through special courses how chip design can be applied to different domains. Furthermore, DTU's flexible curriculum also allows for easy integration of international mobility. The second and third semesters are recommended as the optimal window for exchange, allowing students to participate in mobility programs at one of the partner universities, as well as other universities.

In terms of career preparation, the program's combination of theoretical foundations, practical skills, and hands-on experience through the chip design project and Master's Thesis ensures that students are equipped to meet the industry demands. We expect graduates to pursue careers as chip design engineers, verification engineers, system architects, or R&D engineers, with many using their thesis projects (particularly those conducted in collaboration with industry) as a direct gateway to professional roles.

### Institut Mines-Télécom (IMT) – École des Mines de Saint-Étienne

IMT is integrating the Edu4Chip programme concept in Chip Design into its existing ISMIN – Master's Degree in Microelectronics and Computer Science from Mines Saint-Etienne (a French engineering diploma). IMT is also implementing in Edu4Chip a new one-year post-Master programme (a French Master Spécialisé) – Advanced Master in Microelectronics Circuit Design/Mastère Spécialisé Designer de Circuits Microélectroniques, or MS CCM. The new MS CCM programme has been approved and will start in October 2025 at Mines Saint-Etienne.

#### Programme Structure at ISMIN Curriculum

The ISMIN Curriculum has a duration of 3 years, the last 2 years corresponding to an MSc programme, each year is divided into 2 semesters. The programme has a total of 180 credits, with 30 credits allocated to each semester. Due to its duration, the implementation of Edu4Chip in the ISMIN Curriculum differs slightly from how the Programme concept is applied by the other partner universities, although the objectives and expected outcomes are the same. The outline of the ISMIN curriculum in relation to the Edu4Chip programme concept is shown in Figure 2.

Several tracks (Microelectronics, Computer Science, or Embedded Systems) are offered to the ISMIN students. About a quarter of the approximately 100 students, may join the Edu4Chip programme. To qualify for the Edu4Chip programme, they must follow the Microelectronics major (MSc semester 9, 170h, 11 credits) and a dedicated Chip Design tape-out project (from semester 6 to 9 with several ASIC related projects covering the topic from the first design steps to an actual tape-out). The integration of the Edu4Chip programme involves the adaptation of selected existing courses and the development of new courses (highlighted in purple in Figure 2).

During the first year (semesters 5 and 6), students take compulsory courses in Electrical Engineering, Digital and Analogue Electronics, Computer Science and Physics to build a strong scientific background. They also begin to take more specialized courses in microelectronics, such as a course and project in

|                                                                               |                                                                                                             | Edu4Chip Progra                                                                          | m concept                                                                    |                                                                                  |                                                      |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------|--|

| Lectures Term 1<br>Basic Chip Design                                          |                                                                                                             |                                                                                          | Term 2<br>Frontend Design                                                    | Term 3<br>Backend Design                                                         | Term 4<br>MSc thesis                                 |  |

| Chip design ta                                                                | ape-out project                                                                                             | HDL lab                                                                                  | Frontend Lab                                                                 | Backend Tape<br>out                                                              | Test                                                 |  |

| Edu4Chip Program at IMT, Mines Saint-Etienne, ISMIN engineering diploma (MSc) |                                                                                                             |                                                                                          |                                                                              |                                                                                  |                                                      |  |

| Semester 5                                                                    | Sem. 6                                                                                                      | Sem. 7                                                                                   | Sem.8                                                                        | Sem. 9                                                                           | Sem. 10<br>Internship                                |  |

| digital elec.<br>Electrical eng. courses<br>Computer sc., Physics,            | HDL (Sys Verilog, RTL)<br>Computer arch. 1<br>Embedded prog.<br>Computer sc., Physics,<br>and other courses | <b>Computer arch. 2</b><br>Embedded prog.<br>Computer sc., Physics,<br>and other courses | FPGA project<br>ASIC project (opt.)<br>Other courses<br>(computer sc., etc.) | Microelectronics Maj.<br>Other courses<br>Workshop (1w)<br>Research project (1m) | Internship (at a<br>company or a<br>research center) |  |

| Tape-out project                                                              | HDL                                                                                                         | . Lab                                                                                    | Frontend Lab                                                                 | Backend Lab<br>+ Tape-out                                                        | est                                                  |  |

Etienne.

Hardware Description Languages and an introductory course in Computer Architecture (which are part of the Edu4Chip programme).

In the second year, students take an advanced Computer Architecture course (with labs using System Verilog HDL) and choose 2 elective projects in FPGA and ASIC design (4 and 13 credits respectively). The 2<sup>nd</sup> year programme also includes a number of compulsory courses in management, embedded systems, electronics and other STEM-related courses, totalling 60 credits.

During the 3<sup>rd</sup> year, students following the Edu4Chip programme must follow the elective Microelectronics major (141h, 11 credits, 9<sup>th</sup> semester). It has two tracks covering the physics of semiconductors and the design of integrated circuits: (1) Design methodology track, and (2) Microelectronics basics track.

Design methodology track

- 1. Advanced design of analogue circuits

- 2. ASIC specific circuit design

- 3. FPGA Co-design

- 4. HDL synthesis & modelling

Microelectronics basics track

- 1. Introduction to analogue design

- 2. Digital circuits design

- 3. Semi-conductor physics and components

- 4. Circuit manufacturing methods

- 5. Advanced simulation and verification

The Chip Design Tape-Out project spans the ISMIN curriculum from the 5th to the 9th semester. The HDL and Computer Architecture projects of the 6th and 7th semesters cover the HDL lab part. The Frontend Lab consists of two elective FPGA and ASIC projects in the 8th semester (year 2). The final part of the tape-out project (backend design, tape-out and test of the manufactured chip) takes place in the 3rd year. It is structured around a dedicated workshop and research project.

These courses and projects ensure that students gain both theoretical knowledge and practical experience in the design, implementation, verification and testing of digital or analogue circuits. They benefit from the multi-semester Chip Design tape-out project, which provides practical experience of actual chip design and a full understanding of the chip design process.

#### Relation between Structure and Competencies at ISMIN

Following the Edu4Chip programme in Chip design implies that students select several elective courses from the ISMIN curriculum to ensure that they effectively learn the art of integrated circuit design from its theoretical basics to its more advanced competencies and practical experience up to an actual tapeout.

A complete set of theoretical skills in microelectronics is taught from semesters 5 to 9, following specific courses and especially in the 3rd year of the Microelectronics major. This includes a comprehensive grounding in analogue and digital design and computer architecture in the first year (including HDL and computer architecture courses). Additional competencies in digital design and computer architecture are provided in the 2nd year. The more advanced competencies related to chip backend design and design verification and testing are covered in the 3rd year Microelectronics major. More general embedded systems, computing and electronics courses can be selected from a wide range of elective courses and modules.

Gaining practical experience in chip design is central to the Edu4Chip programme. This is achieved through hands-on projects linked to the core design courses. This contributes to the multi-semester chip design tape-out project, which aims to provide students with a full set of practical chip design competencies and a full understanding of the chip design process. To achieve this, students follow a dedicated ASIC design track that takes them through the main steps of a chip design. Starting from a high-level specification, they will design their own student IP from HDL modelling through frontend and backend steps to tape-out. The ASIC design track will be taught in groups of 4-5 students through different projects during the semesters of their curriculum (semester 5 & 6: HDL description and validation, semester 7: front-end, semester 8: back-end, tape-out and test of the fabricated ASIC; note that testing could be delayed to semester 10 due to manufacturing delays). Student projects will mainly focus on hardware security, hardware acceleration and processor implementation with an emphasis on RISC-V architectures (other topics can also be chosen).

Students also receive formal training in English (or other foreign elective languages), management, project planning, group work and entrepreneurship during the 3 years of the ISMIN curriculum (an average of 10 credits per semester).

The third year (semester 10) ends with an internship in a company or research centre. The aim is to provide students with practical work experience. Ideally, students on the Edu4Chip programme will apply their new chip design skills to an industrial or research chip design problem.

A full and detailed description of the ISMIN curriculum can be found at: <u>https://www.mines-</u> stetienne.fr/en/academic/ismin-masters-degree-in-microelectronics-and-computer-science/

#### Programme Structure at MS CCM Curriculum

This one-year postgraduate programme is delivered on an apprenticeship basis. It is open to MSc graduates in Electrical Engineering, Computer Science and other related scientific fields with a focus on Electrical Engineering or Physics. Students are admitted to the programme on the basis of their academic record and curriculum. They are required to find a host company for their apprenticeship.

Students follow their academic courses while being employed by a company. The academic courses represent a total of approximately 400 hours in our school (15 full weeks), the remaining time is dedicated to gaining industrial experience in the field of microelectronics in the host company. The MS CCM courses follow the main organisation of the Edu4chip Master's programme concept: it focuses on chip design and includes the design, tape-out and testing of an integrated circuit by the students. A key aim of this programme is to attract STEM-related MSc students without a chip design background and give them the opportunity to specialise in microelectronics.

The academic courses (detailed in Table 1) are compulsory, they represent a total of approximately 400 hours in our school (45 credits, 5 modules covering the whole topic of microelectronics and chip design).

| Adv. Master program – Courses description. – Micr                 | oelectronics Circo  | uit Design 45 credits/406h              |

|-------------------------------------------------------------------|---------------------|-----------------------------------------|

| Module 1 – Basics 84h                                             |                     |                                         |

| <ul> <li>Basics of digital and analog electronics, rem</li> </ul> |                     |                                         |

| <ul> <li>Semiconductor physics – 21h</li> </ul>                   |                     |                                         |

| <ul> <li>Semiconductor device – 28h</li> </ul>                    |                     |                                         |

| <ul> <li>Process and manufacturing – 14h</li> </ul>               |                     |                                         |

| Module 2 – Digital and analog design                              | 91h                 | Module 5                                |

| <ul> <li>Digital design – 35h</li> </ul>                          |                     | ASIC Design                             |

| <ul> <li>Analog design – 35h</li> </ul>                           |                     | 70h                                     |

| <ul> <li>Processor architecture – 21h</li> </ul>                  |                     | , , , , , , , , , , , , , , , , , , , , |

| Module 3 – IC design flow                                         | 91h                 |                                         |

| <ul> <li>HDL synthesis – 35h</li> </ul>                           |                     |                                         |

| <ul> <li>Advanced simulation and verification – 21h</li> </ul>    |                     |                                         |

| <ul> <li>Co-design and FPGA prototyping – 35h</li> </ul>          |                     |                                         |

| Module 4 – Applied and domain specific courses                    | 70h                 |                                         |

| <ul> <li>Low power and energy harvesting – 35h</li> </ul>         |                     |                                         |

| <ul> <li>NMOS fabrication lab – 35h</li> </ul>                    |                     |                                         |

| Company side programme – work experience                          |                     | 30 credits                              |

| • Thesis – 15 credits                                             |                     |                                         |

| <ul> <li>Company work – 15 credits</li> </ul>                     |                     |                                         |

| Table 1. Advanced Mester Misseelectropics Circ                    | 11 D 1 1 10 0 0 0 1 | 0 1 1 1                                 |

Table 1: Advanced Master Microelectronics Circuit Design/MS CCM, Courses description.

The duration of this programme, one year on an apprenticeship basis, does not match the two-year schedule of the Edu4Chip chip design tape-out project. However, a similarly tailored chip design tape-out project (Module 5, ASIC design) is being implemented with the same objective: to design an integrated circuit from HDL description to actual fabrication and test. To this end, students will participate in the Tiny Tapeout initiative (https://tinytapeout.com) or a similar open silicon initiative that allows them to design their own digital IP and embed it in a test chip to be fabricated.

The company side programme (30 credits, approximately 6 months) is designed to provide students with real work experience in microelectronics and chip design. It also aims to facilitate their professional integration into a microelectronics company (a key objective of the Edu4Chip project). The in-company programme involves the writing of a Master's thesis describing the professional project carried out in the host company (it benefits from academic supervision). Students must be careful to generalise their thinking by not focusing solely on the case of their host company. Defended in front of a jury, this exercise enables students to structure their thinking by studying a microelectronics case study in depth and presenting it with clear and precise arguments.

#### Relation between Structure and Competencies at MS CCM

The MS CCM curriculum is open to MSc graduates in Electrical Engineering, Computer Science, Embedded Systems and other STEM related courses on the basis of their academic record and curriculum. The technical knowledge acquired in their previous MSc curriculum, together with skills such as the ability to work independently or in groups, to discuss possible solutions, to conduct literature research and to communicate, will enable them to make the most of the proposed courses and company work.

In Module 1, after an 'on-boarding' course in digital and analogue electronics, students take courses in semiconductor physics, devices and microelectronics manufacturing processes, which provide a foundation for the more chip design focused courses. Module 2 covers digital and analogue design skills and modern computer architectures. It includes laboratory work using industry-standard CAD tools. It serves as a foundation for Module 3, which covers the full integrated circuit design flow from front-end to back-end tasks. Module 4 extends the student's skills with an applied course and project on low power IC design and energy harvesting. As a good understanding of the manufacturing processes and their constraints is essential to become an expert chip designer, students also undertake a week's NMOS fabrication training in a clean room. Students also work on a chip design as part of their studies (Module 5). This practical project ensures that students develop a coherent understanding of ASIC design. It is designed around the idea that all students on the MS programme will design an integrated circuit, take part in a tape-out and measure their chips during the course of the programme. This part of the more theoretical chip design courses and labs aims to provide the foundation for the full range of competencies of an expert chip designer from the Edu4Chip programme.

Working in a microelectronics company and defending a Master's thesis aims to provide students with problem-solving skills in the field by carrying out a practical industrial or research project. Students will apply the theoretical and practical approaches and scientific methods they have learnt in their courses. In addition to the practical activities, it includes many planning and conceptual tasks related to the professional life or work of engineers in chip design, which will complete the set of competencies they will acquire.

A complete description of MS CCM can be found at: <u>https://www.mines-stetienne.fr/formation/</u> <u>mastere-specialise-concepteur-de-circuits-microelectroniques/</u>

# KTH Royal Institute of Technology (KTH)

KTH implements in Edu4Chip a new track "Embedded Electronics" in the Embedded Systems Master Program. The program syllabus for the new track was approved and will start in August 2025.

#### Formal Structure

The Embedded system Master Program has a duration of 2 years. Each year is divided in 2 semesters, and each semester is divided in 2 periods. Students entering the program require a background on Electrical Engineering or Computer Science. At the end of the program the students receive a MSc degree. The Embedded Electronics track focuses on ASIC design, and it is designed around the idea that all students in the track will design integrated circuits, participate in a tape out, and measure their chips during the duration of the program. The ambition is that students finishing the program will have a strong background in both analogue and digital circuits and the irreplaceable set of skill and experience that is only acquired after participating in all phases of ASIC design including tape-out and measurement of the chips. The syllabus of the track is divided is as follows.

During the first semester of year 1 (periods 1 and 2), there are 4 compulsory courses covering an introduction to integrated circuits and microelectronics, digital circuits design flows, and analogue circuits design flow.

During the second semester of year 1 (periods 3 and 4), the students take a compulsory project course in ASIC design in which they design digital and/or analogue circuits using all the knowledge and skills acquired in the first semester. These circuits will be sent to fabrication at the end of the second semester. The plan for this course is to involve industrial partners for invited lectures, design reviews, etc. At the same time the students take 2 elective courses. Here students have the freedom to choose specialization courses in the area of RFIC/MMIC and mixed-signal, digital system design and computer architectures. They can also choose courses on nanofabrication technologies.

During the first semester of year 2 (period 1 and 2), the students take compulsory courses: research methodology, embedded systems, and Electronic System Design. In the last course, they will measure packaged samples of the ASICs they designed in the previous semester. There is also a slot for one elective course.

The second semester of year 2 is devoted to thesis work.

The program has a total of 120 credits, with 15 credits allocated for each period. Each course has 7.5 credits. with the exception of the course project on ASIC design which has 15 credits. The program comprises:

- (I) 8 compulsory courses with a total of 67.5 credits

- (II) 3 elective courses with a total of 22.5 credits

- (III) Thesis of 30 credits (20 weeks)

|        | P1                                                                                             | P2                                                       | P3                                                                     | Р4       |

|--------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|----------|

| Year 1 | IL2234 – Digital Systems<br>Design and Verification<br>using Hardware Description<br>Languages | IL2225 – Embedded<br>Hardware Design in ASIC<br>and FPGA | IL2244 – Project Course in Application Specific Integrated<br>Circuits |          |

|        | IL2241 – Introduction to<br>Integrated Circuits                                                | IL2242 – Analog Integrated<br>Circuits                   | Elective                                                               | Elective |

| Year 2 | II2211 – Research<br>Methodology and Scientific<br>Writing for Embedded<br>Systems             | IL2237 – Electronic Systems<br>Design                    | Thesis                                                                 |          |

|        | IL2206 – Embedded<br>Systems                                                                   | Elective                                                 |                                                                        |          |

Table 2: Structure of specialization direction at KTH

https://www.kth.se/student/kurser/program/TEBSM/20252/arskurs1?l=en

#### **Relation between Structure and Competences**

The track is structured so that the 4 compulsory courses at the beginning of the program (semester 1) provide the minimum competences that are required to participate in the tape-out of a mixed-signal ASIC. In the first period, students are required to take an introductory course on integrated circuits which covers topics such as fabrication and scaling of CMOS technology, hierarchical design, chip interconnects, and design methodologies. At the same time, they study digital system design using HDL and verification which has a strong focus on the digital front-end. The next two courses are a digital ASIC design covering methodologies for the digital back-end, and a course on analog integrated circuits. The rationale behind this is that modern SoCs contain both analog and digital circuits. Nowadays, it is seldom possible to find a purely digital or analog ASIC. Therefore, a good background in both analog and digital design is fundamental.

The ASIC project course is the core of the track. The students will receive formal training in project management, project planning, and group work. They will be tutored by experienced designers from companies in the Stockholm area. Therefore, they will also be exposed to industrial environments and valuable networking opportunities.

After sending the chip to fabrication, the students take the course on scientific methodology and writing which give them a solid background to carry out their master thesis work. At the same time,

they take a course on embedded systems which is very important since the students will need to mount their ASIC to an embedded system in order to perform measurements and validation tests.

At the end of the program, they will take a course on electronic system design which will give them the competences that are necessary to design and fabricate PCBs, mount components including the ASIC samples, and perform measurements in the lab.

Finally, the track includes 3 elective courses that give the students the opportunity to specialize in a particular field. Some of these courses, i.e. our RFIC course, are organized in cooperation with the industry.

# Tampere University (TAU)

Tampere University implements Edu4Chip concept into the existing Master's Programme in Computing Sciences and Electrical Engineering. A new specialization module Advanced Studies in System-on-Chip Design was created to offer the Edu4Chip track inside the MSc program. A limited set of computer engineering and System-on-Chip courses is also offered for students in other MSc programs and specializations such as Embedded Systems and Digital Design in Robotics.

The Advanced Studies in System-on-Chip Design module started in August 2024, but not all courses were implemented during the first academic year. The module is expected to be fully running with all the course implementations during the academic year 2025-2026.

#### **Program Structure and Requirements**

A MSc program in Tampere University has a duration of 2 years. Each year is divided into autumn and spring semesters and semesters are further divided in 2 periods, totaling to 4 periods plus a summer period for possible intensive courses. Courses are generally 5 ECTS credits each and can be scheduled for either 1 or 2 periods. The MSc degree in Computing Sciences and Electrical Engineering consists of 120 credits divided as follows:

- Joint Studies (9-15 credits)

- Advanced Studies Module, including the Master's Thesis (at least 80 credits)

- Free Choice Study Module and Free Choice Course Units

The Joint Studies include the mandatory courses Tools for Theses (5 credits) and Orientation to Master's Studies and Professional Life (3 credits) by minimum. Students who completed their Bachelor's degree outside of Finland are also required to take at least the A1 level course in Finnish (3 credits) and Thesis Writing B (2 credits). The module should be completed by selecting at least one additional 1-2-credit course. The available courses are related to communications, working life, and well-being.

The Advanced Studies module includes 50 credits of specialization-specific studies and the Master's Thesis (30 credits). Specializations can have different number of mandatory courses, leaving more or less freedom for students in their personal study plan. The Master's Thesis is done typically in the spring semester of the second year.